Un nuevo transceptor inventado por ingenieros eléctricos de la Universidad de California en Irvine aumenta las frecuencias de radio al territorio de los 140 gigahercios, desbloqueando velocidades de datos que rivalizan con las de los cables físicos de fibra óptica y sentando las bases para una transición a los protocolos de transmisión de datos 6G y FutureG. Para crear el transceptor, investigadores de la Escuela de Ingeniería Samueli de la Universidad de California en Irvine diseñaron una arquitectura única que combina el procesamiento digital y analógico. El resultado es un sistema de chip de silicio, compuesto por un transmisor y un receptor, capaz de procesar señales digitales con mucha mayor rapidez y eficiencia energética que las tecnologías disponibles anteriormente.

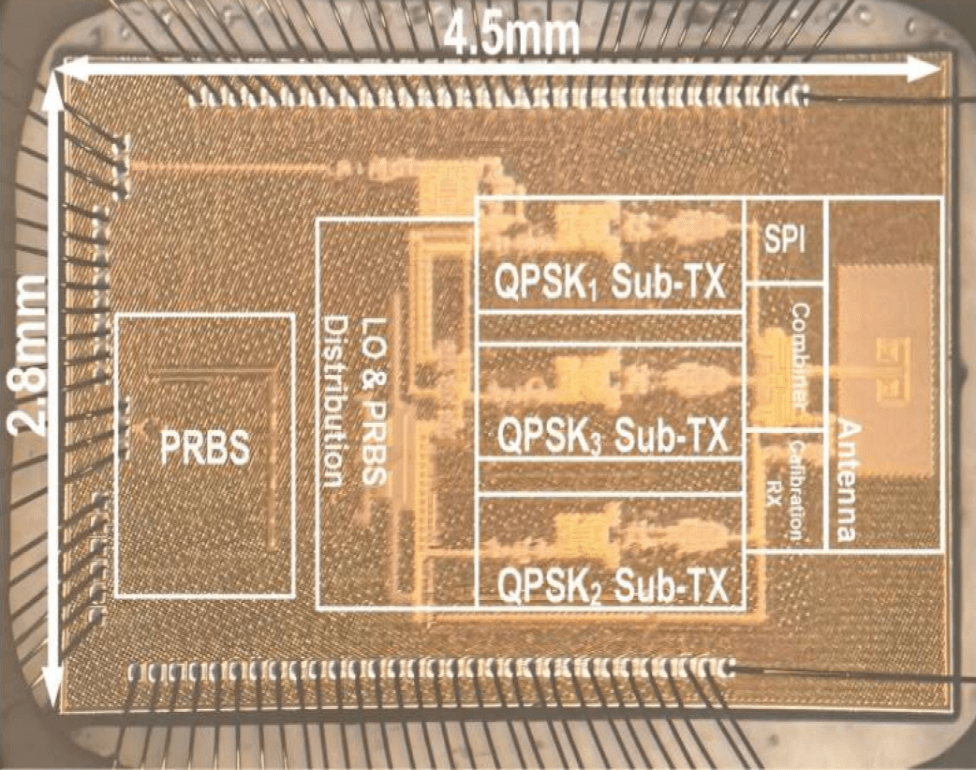

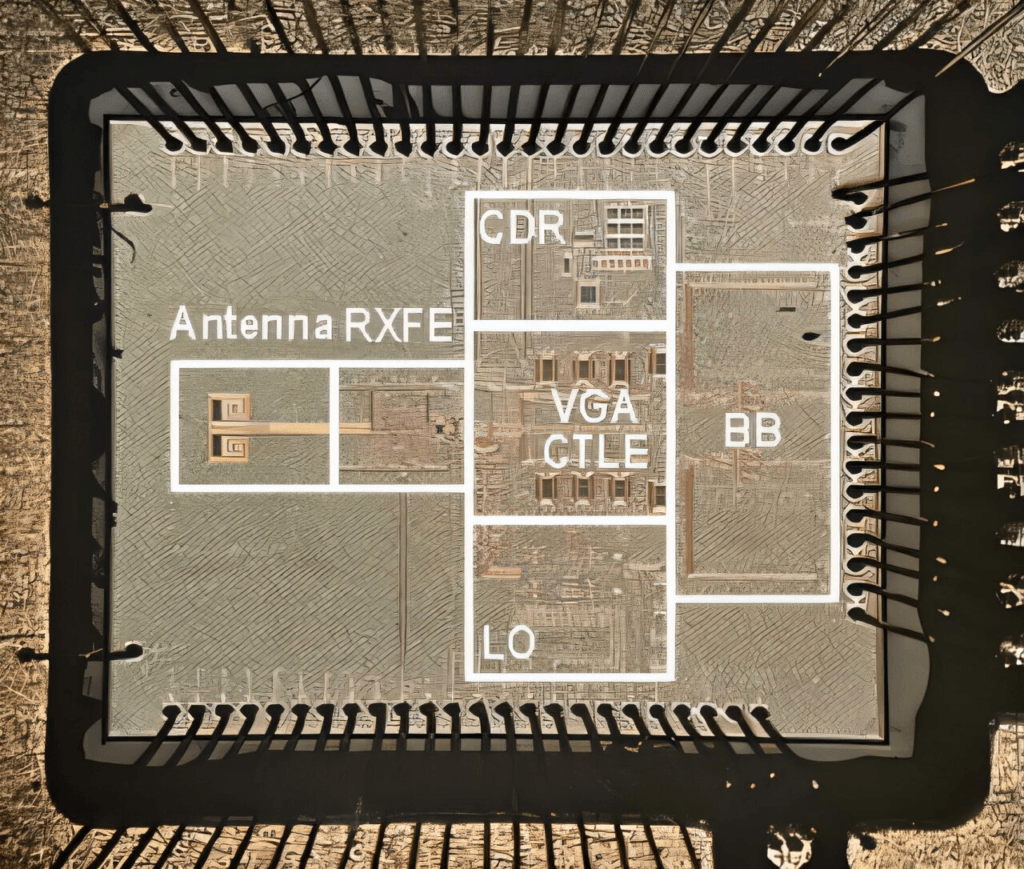

El equipo del Laboratorio de Circuitos Integrados de Comunicación a Nanoescala de la UC Irvine describe su trabajo en dos artículos publicados este mes en la revista IEEE Journal of Solid-State Circuits. En uno, los ingenieros analizan la tecnología que denominan transmisor “bits-a-antena“, y en el segundo, su receptor “antena-a-bits“.

“Llamamos a esta tecnología ‘cable de conexión de fibra inalámbrica’ porque ofrece la velocidad ultrarrápida de la fibra óptica sin los cables físicos”, afirmó Payam Heydari, director de NCIC Labs, profesor de ingeniería eléctrica e informática del rector de la UC Irvine y autor principal de ambos artículos. “Al operar en la banda F —un rango de frecuencia muy superior a los estándares actuales del 5G—, podemos ofrecer anchos de banda masivos que transformarán la comunicación entre máquinas, robots y centros de datos”.

Afirmó que este avance es la culminación de una visión estratégica a largo plazo. Su equipo comenzó a formular el concepto de bits a antena en 2020 tras reconocer que las arquitecturas tradicionales de chips de señal mixta, que dependen en gran medida de convertidores de datos de alto consumo energético, eventualmente se toparían con un límite de rendimiento.

Enfoques innovadores para el diseño de circuitos

“Nos dimos cuenta de que para alcanzar el esquivo hito de los 100 gigabits por segundo —que es 100 veces la velocidad de los dispositivos inalámbricos actuales— sin que el chip se quemara, teníamos que replantearnos fundamentalmente la topología del circuito”, dijo Heydari. “Imaginamos arquitecturas novedosas, totalmente analógicas, que pudieran superar los graves problemas de consumo de energía que afectan a los diseños de alta velocidad”.

Los miembros del equipo comprendieron que, a medida que aumentaban las velocidades, la frontera entre lo digital y lo analógico debía cambiar. Al trasladar la mayor parte del trabajo al ámbito analógico, pudieron superar las ineficiencias que limitan los chips 5G estándar. Heydari afirmó que los investigadores académicos y los ingenieros de comunicaciones se han enfrentado durante mucho tiempo a un cuello de botella: a medida que aumentan las velocidades inalámbricas, la potencia necesaria para procesar esos datos suele dispararse.

“Si nos apegáramos a los métodos tradicionales, la duración de la batería de los dispositivos de nueva generación se agotaría en minutos”, afirmó. “La respuesta de nuestro grupo es un transceptor que supera las limitaciones actuales al realizar cálculos complejos en el dominio analógico, en lugar del dominio digital, que consume mucha energía”.

El nuevo transceptor de extremo a extremo funciona a 120 gigabits por segundo, lo que es lo suficientemente rápido para transferir múltiples películas 4K en un abrir y cerrar de ojos.

Superar los desafíos del transmisor y el receptor

“La Comisión Federal de Comunicaciones y los organismos de normalización 6G están considerando el espectro de 100 gigahercios como la nueva frontera”, dijo Zisong Wang, ex investigador doctoral de la UC Irvine en ingeniería eléctrica y ciencias de la computación que ahora trabaja en Marvell Technology Inc. y es el autor principal del artículo sobre bits a antena.

“Pero a tales velocidades, los transmisores convencionales que crean señales utilizando convertidores de digital a analógico son increíblemente complejos y consumen mucha energía y se enfrentan a lo que llamamos un cuello de botella DAC”.

Dijo que el nuevo transmisor del equipo elimina por completo el DAC al generar señales directamente en el dominio de radiofrecuencia mediante tres subtransmisores sincronizados. “Es como preparar una maleta a la perfección antes de salir de casa, en lugar de intentar organizarla mientras se corre al aeropuerto”, dijo Wang.

Mohammad Oveisi, estudiante de doctorado de la UC Irvine y coautor del artículo sobre la conversión de antena a bits, explicó que este método, conocido como dominio RF 64QAM, permite que el chip sea increíblemente eficiente, enviando más datos sin sobrecalentarlo. Contar con transmisores y receptores capaces de procesar datos de tan alta frecuencia será vital para dar paso a una nueva era dominada por productos conectados a internet, vehículos autónomos y computación perimetral con IA, que permite ejecutar aplicaciones de inteligencia artificial y aprendizaje automático en dispositivos locales.

Abordar las limitaciones y la eficiencia del receptor

Si bien este sueño digital ha impulsado a los desarrolladores de tecnología durante décadas, aparecieron obstáculos, según el autor principal del artículo de antena a bits, Youssef Hassan, ex investigador de doctorado en ingeniería eléctrica y ciencias de la computación de la UC Irvine, actualmente en Qualcomm.

“Los receptores tradicionales tienen dificultades para captar datos tan rápidos sin usar componentes masivos y de alto consumo, llamados convertidores analógico-digitales”, explicó. “La ley de Moore sugiere que podemos simplemente reducir el tamaño de los transistores para ir más rápido, pero a estas velocidades extremas, nos topamos con un obstáculo físico conocido como cuello de botella de muestreo. Digitalizar una señal de 120 Gbps suele requerir convertidores analógico-digitales masivos que consumen muchos vatios de potencia, una cantidad excesiva para un teléfono inteligente”.

En lugar de intentar forzar a los componentes electrónicos a trabajar más, el equipo diseñó un receptor que trabaja de forma más inteligente.

“Desarrollamos una técnica llamada demodulación analógica jerárquica”, explicó Hassan. “Al descomponer la señal jerárquicamente en el dominio analógico, separando las complejas capas de datos antes de digitalizarlas, extraemos los datos utilizando una fracción de la energía que normalmente se requiere”.

Señaló que el chip receptor, fabricado con tecnología de silicio sobre aislante de 22 nanómetros totalmente agotado, consume sólo 230 milivatios de energía, lo que lo hace lo suficientemente eficiente para dispositivos portátiles.

Impacto potencial y aplicaciones futuras

Heydari dijo que además de permitir la transmisión en el rango de 140 gigahercios, la arquitectura de bits a antena del transceptor permite que se produzca en masa a un menor costo, allanando el camino para una adopción generalizada.

“Nuestra innovación elimina la necesidad de kilómetros de cableado de cobre complejo dentro de los centros de datos”, afirmó. “Los operadores de granjas de datos pueden establecer enlaces inalámbricos ultrarrápidos entre racks de servidores, ahorrando considerablemente en hardware, refrigeración y energía”.

Heydari agregó que se utilizaron servicios rutinarios de fabricación de semiconductores para apoyar este proyecto de investigación, demostrando que estos chips de alto rendimiento se pueden construir utilizando procesos de fabricación estándar.

Fuente: Tech Xplore.